|

КОНТАКТЫ |

|

| |

Тел. (391) 290 44 77

E-mail: sales@vsemcomp.ru

ОТПРАВЛЯЙТЕ ЗАЯВКИ НА ПОЧТУ, т.к. временно не работает форма заказа

Подпишись на наш Телеграмм

г.Красноярск, ул.Мечникова, д.44А, оф.139

Работаем с 10:00 до 19:00

Выдача товара с с 12:00 до 17:00

Выходной: сб, вс |

|

|

Типы оперативной памяти

|

- Краткие описания:

- Ссылки на подробности и термины:

|

|

По материалам с сайта www.fcenter.ru »

Необходимость в изменении технологии серверной памяти возникла вот в связи с

чем. Чем дальше, тем выше частоты модулей, используемых в серверах. Но с ростом

их частоты возникает большое число проблем, связанных с такими физическими

эффектами, как всевозможные наводки и перекрестные помехи. Чем выше частота

работы памяти, тем сложнее с ними бороться. И в результате имеем следующую

ситуацию: чем выше частота работы памяти, тем выше электрическая нагрузка на

контроллер памяти, и тем меньше модулей у нас может работать одновременно.

Поскольку для серверов большой объем поддерживаемой памяти есть одно из ключевых

требований, необходимо как-то выкарабкиваться из этого тупика. Одним из

вариантов такого выхода является технология FB DIMM. |

|

|

Суть FB DIMM вполне описывается словом «сериализация». А сама идеология

находится вполне в современном духе перехода к последовательным шинам везде, где

только можно. В частности, оказалось, что можно и в технологиях, связанных с

памятью.

Идея FB DIMM состоит в том, что от общей шины памяти, на которой сидят модули

памяти, мы уходим. Поэтому избыточная электрическая нагрузка, которую модули

создают на контроллер, перестает быть проблемой. Вместо этого есть две шины

(одна на чтение, другая – на запись) на которых сидят не сами массивы ячеек, а

только управляющие буферы модуля (AMB в терминологии FB DIMM). Таким образом,

питание массивов ячеек контроллером памяти более не осуществляется. Массивы

ячеек основаны на технологии DDR2, здесь FB DIMM вполне пересекается с текущими

технологиями. Благодаря этому, производителям памяти будет проще перейти на

технологию FB DIMM.

Кроме того, все передачи контроллер памяти ведет только в буферы AMB, все

данные получает оттуда же.

Все это происходит, повторюсь, по узким высокочастотным шинам. Поскольку

технология ECC является присущей абсолютно всем пересылкам данных между AMB и

контроллером, появляются дополнительные преимущества типа защиты команд ЕСС

кодом. В этом плане FB DIMM меньше подвержены ошибкам, поскольку содержат более

развитые технологии контроля ошибок и восстановления данных.

Кроме того, поскольку модуль FB DIMM фактически связан с контроллером только

буфером AMB, для такой памяти гораздо проще достигнуть пропускной способности,

максимально близкой к теоретической. Например, если у нас в наличии два модуля

FB DIMM, мы вполне можем одновременно писать в один и читать из другого.

Кроме всего прочего, использование буфера AMB позволяет полностью скрывать от

контроллера такую служебную операцию, как восстановление содержимого ячейки,

refresh. Можно скрывать и некоторые другие операции. Более того, команды в

модуле FB DIMM конвейеризированы, и можно отдавать следующую команду на фоне

выполнения предыдущей.

К достоинствам отнесем и заметно меньшее число контактов, которые нужно

разводить: в частности, в презентации от Intel (см. ссылку ниже) приводят пример

69 контактов у FB DIMM модуля против 240 у модуля DDR2. Поэтому вместо двух

каналов DDR2 вполне можно разводить четыре канала, и при этом у них разводка

будет занимать меньшее число контактов (276 против 480), и к ней предъявляются

менее жесткие требования. Ну а результат сравнения пропускной способности двух

конкурирующих типов вполне предсказуем: два канала DD2-400 имеют теоретический

максимум 6.4GB/sec, а четыре канала FB DIMM способны выдать порядка

17GB/sec.

Более подробно о FB DIMM » |

|

Основное отличие этого типа памяти от "просто" DDR SDRAM заключается в

реализации целого набора дополнтельных решений, направленных на повышение

надежности и стабильности работы. Именно поэтому, DDR SDRAM REG всегда

использует протокол ECC (Error Checking and Correcting/Проверка и исправление

ошибок).

Как не сложно догадаться, основная область применения этой памяти -

серверы.

Более подробно о: ECC и Registered DIMM » . |

|

|

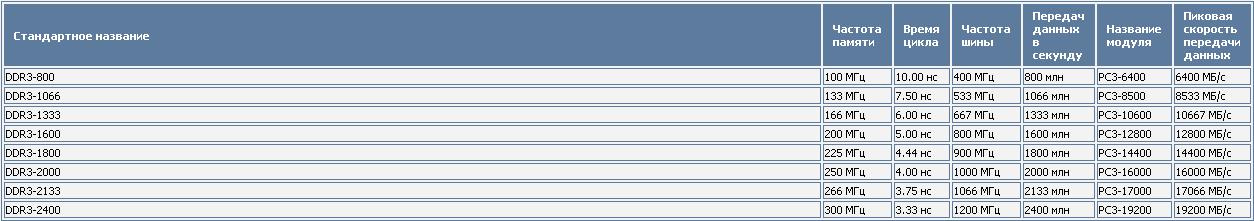

DDR3 SDRAM (англ. double-data-rate three synchronous dynamic random access

memory — синхронная динамическая память с произвольным доступом и удвоенной

скоростью передачи данных, тип 3) — это тип оперативной памяти используемой в

компьютерах, разработанный как последователь DDR2 SDRAM.

DDR3 обещает сокращение потребления энергии на 40% по сравнению с модулями

DDR2, благодаря применению 90-нм (в дальнейшем 65-нм и 50-нм) технологии

производства, что позволяет снизить эксплуатационные токи и напряжения (1,5 В,

по сравнению с 1,8 В для DDR2 и 2,5 В для DDR). "Dual-gate" транзисторы будут

использоваться для сокращения утечки тока. |

|

Чипы и модули

Возможности DDR3 SDRAM компонентов:

- Появление контакта асинхронного сброса

- Support of system level flight time compensation

- Встроенная калибровка портов ввода/вывода

- Калибровка READ и WRITE DDR3 модулей:

- Определение адресов и команд непосредственно в контроллере модуля (fly-by)

- Высокоточные резисторы в цепях калибровки

Преимущества по сравнению с DDR2:

- Более высокая полоса пропускания (до 2400 МГц)

- Увеличенная эффективность при малом энергопотреблении (более длительное

время работы батарей в ноутбуках)

- Улучшенная конструкция, способствующая охлаждению

Недостатки по сравнению с DDR2:

- Обычно более высокая CAS-латентность, но

компенсируемая высокой полосой пропускания, таким образом увеличивающаяся полная

производительность в определённых приложениях

|

|

По материалам с сайта wikipedia.org

» |

|

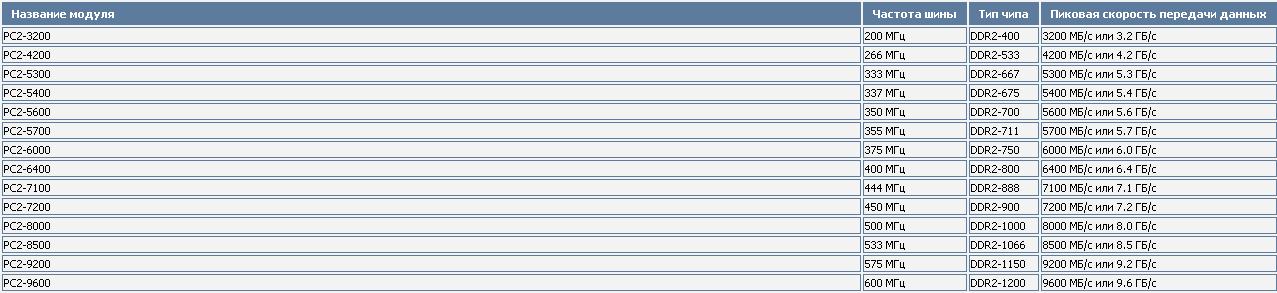

DDR2 SDRAM (англ. double-data-rate two synchronous dynamic random access

memory — синхронная динамическая память с произвольным доступом и удвоенной

скоростью передачи данных, тип 2) — это тип оперативной памяти используемой в

компьютерах в качестве оперативной и видеопамяти. |

|

|

Как и DDR SDRAM, DDR2 SDRAM использует передачу данных по обоим срезам

тактового сигнала, за счёт чего при такой же частоте шины памяти, как и в

обычной SDRAM, можно фактически удвоить скорость передачи данных (например, при

работе DDR2 на частоте 100 МГц эквивалентная эффективная частота для SDRAM

получается 200 МГц). Основное отличие DDR2 от DDR - вдвое большая частота работы

шины, по которой данные передаются в буфер микросхемы памяти. При этом, чтобы

обеспечить необходимый поток данных, передача на шину осуществляется из четырёх

мест одновременно. Итоговые задержки оказываются выше, чем для DDR.

DDR2 не является обратно совместимой с DDR, поэтому ключ на модулях DDR2

расположен в другом месте по сравнению с DDR и вставить модуль DDR2 в разъём

DDR, не повредив последний (или первый), невозможно.

Более скоростные модули DDR2 совместимы с более медленными, при этом работа

возможна на частоте самого медленного модуля системы.

Модули

Преимущества по сравнению с DDR:

- Более высокая полоса пропускания

- Как правило, меньшее энергопотребление

- Улучшенная конструкция, способствующая охлаждению

Недостатки по сравнению с DDR:

|

|

По материалам с сайта wikipedia.org

» |

|

DDR SDRAM (double data rate SDRAM) отличается от обычной SDRAM тем, что на

той же частоте имеет вдвое большую пропускную способность. |

|

|

По принципам работы она похожа на SDRAM, но, в отличие от нее, может

принимать и передавать данные на обоих фронтах тактовых импульсов. Это удваивает

скорость передачи данных. Кроме того, в DDR RAM используется протокол DLL (Delay

Locked Loop), позволяющий сдвинуть во времени интервал действительного значения

выходных данных. Таким образом сокращаются простои системной шины при считывании

данных на нее из нескольких модулей памяти.

Правда, речь идет только о передаче потока данных, тогда как запросы на их

получение поступают с той же скоростью, что и у SDRAM (конечно, только если

говорить о работе на одной и той же частоте). Представьте, что вы задаете

вопросы, а отвечают вам со скоростью вдвое большей, чем вы спрашиваете. Если у

вас несколько достаточно «емких» вопросов (компьютерные игры обращаются к памяти

нечасто, запрашивая пересылку больших объемов информации), ответы на них будут

получены, скажем, вместо получаса всего за пятнадцать минут. Но если ваши

вопросы коротки и многочисленны, а ответ на них ожидается в виде «да» или «нет»

(так «поступают» офисные приложения), проку от скорости источника информации

будет не слишком много.Таким образом, компьютерные игры работают на DDR SDRAM

значительно быстрее (хоть и не в два раза), а разница на офисных приложениях не

так заметна. Спецификации DDR-памяти получили название не по частоте, как в

случае SDRAM, а по пропускной способности, измеряемой мегабайтами в секунду, -

PC-2100 (266 МГц), PC-2700 (333 МГц) и PC-3200 (400 МГц).

DDR SDRAM - оптимальное решение для любой современной системы, вне

зависимости от того, построена она на процессоре Intel или AMD. Покупая

DDR-память, следует отдавать предпочтение продукции только известных

производителей. Это связано с тем, что не все производители второго звена строго

следуют спецификациям.

Устанавливать DDR SDRAM в систему на Рentium III или Celeron вряд ли

оправданно. В то же время для Athlon и Pentium 4 это практически

безальтернативное решение по соотношению цены и

качества. |

|

Технология RDRAM (Rambus) представляет собой 16bit шину данных и

результирующую частоту до 1066 МГц. Узкая шина и колоссальная частота

значительно повышают эффективность использования памяти и загрузку, максимально

освобождая протокол от временных задержек. |

|

|

Rambus DRAM (DRAM от фирмы Rambus) - чемпион по рабочей частоте. Ее

внутренняя тактовая частота - 400 МГц, результирующая - 800 (при передаче

данных).

Серьезному (хотя бы в два раза) отрыву от конкурентов мешает узкая шина -

всего 16 разрядов вместо 64 у прочих типов памяти: мы можем бежать к выходу из

помещения сколь угодно быстро, но если нам в конце придется с трудом, тратя

драгоценное время, протискиваться через узкую дверь, а у медленных конкурентов

выход широк и свободен, то снаружи мы окажемся не в два-три раза быстрее

соперников, а с гораздо меньшим отрывом. Тем не менее, Rambus DRAM благодаря

высокой тактовой частоте имеет высокое быстродействие: выигрыш в

производительности по сравнению с аналогичной системой на SDRAM составляет 5-10

процентов, а в трехмерных играх - 30-35 процентов.

Важное достоинство Rambus DRAM - стабильное качество вне зависимости от

производителя: фирма Rambus, владелец лицензии и эксклюзивный партнер Intel,

тщательно отбирает компании-лицензиаты.

Модули RIMM, в которых выпускается Rambus SDRAM, в отличие от DIMM,

устанавливаются попарно, подобно памяти EDO и FPM в старых Pentium-системах.

Если на системной плате останутся свободные разъемы под память, необходимо

установить специальные заглушки (для других типов памяти этого не

требуется).

Перспективы развития этого типа памяти неясны. По крайней мере, уже

достаточно давно не появлялось новых наборов микросхем поддерживающих эту

технологию. |

|

Используется в качестве процессорного кэша. Намного дороже и быстрее DRAM (в

частности из-за того, что не требует затрат времени на регенерацию

содержимого). |

|

Следующим оригинальным решением, увеличившим частоту работы SDRAM, явилось

создание кэша SRAM на самом модуле динамического ОЗУ. Так появилась спецификация

Enhanced SDRAM (ESDRAM). Это позволило поднять частоту работы модуля до 200 МГц.

Назначение кэша на модуле точно такое же, что и кэш второго уровня процессора —

хранение наиболее часто используемых данных. |

|

Преимущество синхронного интерфейса —это то, что системные часы задают

временные границы, необходимые DRAM. Это исключает необходимость наличия

множества стробирующих импульсов, обязательных для асинхронного интерфейса. Это,

во-первых, уменьшает трафик по локальной шине (нет "лишних" сигналов), а

во-вторых, позволяет упростить операции ввода-вывода (в операциях пересылки

центральный процессор либо контроллер DMA уже не должен выделять полезную

информацию среди служебных стробирующих импульсов и битов четности). В-третьих,

все операции ввода/вывода на локальной шине стали управляться одними и теми же

синхроимпульсами, что само по себе хорошо.

SDRAM появилась на рынке в 1996 году, а "звездный час" SDRAM настал в 1997

году, после появления чипсета 440BX, работающего на частоте 100 МГц. Вследствие

этого доля рынка SDRAM за год выросла в два раза (с 25% в 1997 году до 50% в

1998 году).

Три стандарта сменилось с тех пор - РС-66, РС-100 и РС-133 (цифра означает

тактовую частоту памяти в мегагерцах), и вплоть до середины 2001 года позиции

SDRAM на рынке казались непоколебимыми - цена доступная, пропускная способность

достаточная, но сегодня, SDRAM практически полностью вытеснена более

производительными типами памяти. |

|

SO-DIMM - разновидность DIMM малого размера (small outline), предназначенных

в первую очередь для портативных компьютеров. Наиболее часто встречаются 72- и

144-контактные модули (32 и 64 бит соответственно). Способ установки аналогичен

SIMM. |

|

|

Аббревиатура DIMM расшифровывается как Dual Inline Memory Module (Модуль

памяти с двойным расположением выводов). В модуле DIMM имеется 168 контактов,

которые расположены с двух сторон платы и разделены изолятором. Таким образом,

DIMM - это не тип памяти, а тип разъема памяти.

Следует отметить, что разъем DIMM имеют много разновидностей DRAM. К тому же

долгон время модули DIMM не имели средств самоконфигурирования (в отличие от

SIMM-модулей). Поэтому для облегчения выбора нужного модуля пользователям на

материнских платах разные типы DIMM имеют от одного до трех вырезов на модуле

памяти. Они предотвращают от неправильного выбора и неправильной установки

модулей памяти. |

|

SIMM - это модуль памяти с однорядным расположением выводов. Модули SIMM

могут иметь объем 256 Кбайт, 1, 2, 4, 8, 16 и 32 Мбайт. Модули SIMM для

соединения с системной платой имеют не штырьки, а позолоченные полоски (так

называемые pin, пины). |

|

CAS-латентность (англ. column address strobe latency) — это время (в циклах)

ожидания между запросом процессора на получение ячейки с информацией из памяти и

временем, когда оперативная память сделает доступным для чтения первую ячейку.

На модулях памяти CAS-латентность обозначается как CAS или CL. Пометка CAS2,

CAS-2, CAS=2, CL2, CL-2 или CL=2 обозначает величину латентности, равную

2. |

|

ECC обычно расшифровывается как Error Checking and Correction, существуют и

другие версии, но смысл заключается в том, что речь идет о схеме обнаружения И

ИСПРАВЛЕНИЯ ошибок в памяти. За счет чего удается добиться таких потрясающих

результатов? Идея, лежащая в основе метода, довольно проста - пусть каждый бит

основной памяти входит БОЛЕЕ ЧЕМ В ОДНУ контрольную сумму. Это потребует

увеличения числа контрольных бит (напомним - стандартный метод контроля четности

реально не требует более 1 контрольного бита на всю шину), но даст возможность

восстанавливать позицию (а, следовательно, и значение) сбойного бита по позициям

несошедшихся контрольных сумм. Предполагается, что контроллер памяти

самостоятельно восстанавливает это значение, не прерывая работу всей системы

(хотя разумно при этом генерировать системное сообщение об исправленной ошибке,

чтобы владелец системы, если такие сообщения повторяются, мог принять меры по

замене памяти, не дожидаясь более значительных сбоев).

Попробуем пояснить на простейшем примере. Представим себе шину из 6 (почему

бы и нет?) бит (1-6), имеющую дополнительно 4 контрольных бита S1-S4, причем в

этих битах хранятся следующие контрольные суммы:

- S1 - 1, 2, 3

- S2 - 1, 4, 5

- S3 - 2, 4, 6

- S4 - 3, 5, 6

Предположим, что в одном из основных бит произошла ошибка, и посмотрим,

ошибку в каких контрольных суммах это вызовет:

- S1, S2

- S1, S3

- S1, S4

- S2, S3

- S2, S4

- S3, S4

То есть по номерам сбойных контрольных сумм сбойный бит определяется

однозначно! Для построения данной схемы использовалась картинка, на которой

основные биты располагаются над главной диагональю квадратной матрицы со

стороной, равной числу контрольных сумм, и каждый бит входит в контрольные суммы

с номером соответствующей строки и столбца этой матрицы. Нетрудно видеть, что

такая схема позволяет с помощью n контрольных сумм "проконтролировать" до

n(n-1)/2 основных бит. 4 контрольные суммы на 6 бит, конечно, выглядят очень

щедро, но при увеличении ширины основной шины требуемое количество контрольных

бит растет всего лишь как (примерно) квадратный корень из нее, так что при

достаточно широких шинах потребность в контрольных битах относительно низка.

Отметим сразу, что нарисованная схема нежизнеспособна по ряду причин.

Предположим, что простой сбой в контрольном бите система может проигнорировать

(так как в этом случае не сойдется лишь одна контрольная сумма). Но рассмотрим,

например, двойную ошибку - скажем, одновременно в битах 1 и 2. Легко видеть, что

результатом будет расхождение в контрольных суммах S2 и S3, что будет

проинтерпретировано как ошибка в бите 4. Аналогично неверную интерпретацию

вызовет ошибка в любых двух битах, неважно, основных или контрольных. В

действительности большинство схем ECC обеспечивает как минимум обнаружение

двойной ошибки (с последующей остановкой системы). Автор не может привести

никакую реализованную в действительности схему ECC, но склонен полагать, что уже

из приведенного примера видно, что никаких чудес здесь нет, причем реализовать

"истинный" ECC можно примерно на том же количестве "лишних" бит (порядка

квадратного корня из удвоенной ширины шины). Можно, например, подумать о схеме,

в которой основные биты не записываются вообще - только набор сумм (слово

контрольных тут не очень подходит), из которых при чтении и восстанавливаются

основные биты (а за счет избыточности - детектируются ошибки). Реально ECC

реализовывалось практически только на 64-битной шине памяти (даже на машинах с

32-битной основной шиной), причем ранние реализации требовали до 16 контрольных

бит, современные же схемы обходятся восемью. |

назад

|